You are here:

AES-ECB 1 Billion Trace DPA Resistant Crypto Accelerator

Rambus Crypto Accelerator AES-AE–Fast Hardware Cores offload compute intensive cryptographic algorithms in SoC’s CPU at 100x performance (when run at identical frequencies) and 10% of the power consumption compared to running the same algorithms in software.

The Crypto Accelerator Hardware Cores offer chipmakers an easy-to-integrate technology-independent soft-macro security solution, offering various levels of cryptographic acceleration performance.

They are easy to integrate into various SoC and FPGA architectures and development flows, and are all designed to maximize performance versus silicon area requirements. The Rambus IP core pass all NIST CAVP vectors. Several of the cores are also available in Differential Power Analysis (DPA) protected versions, extensively validated using the standardized Test Vector Leakage Assessment (TVLA) methodology. These Crypto accelerator cores are portable to any FPGA or ASIC technologies.

The Crypto Accelerator Hardware Cores offer chipmakers an easy-to-integrate technology-independent soft-macro security solution, offering various levels of cryptographic acceleration performance.

They are easy to integrate into various SoC and FPGA architectures and development flows, and are all designed to maximize performance versus silicon area requirements. The Rambus IP core pass all NIST CAVP vectors. Several of the cores are also available in Differential Power Analysis (DPA) protected versions, extensively validated using the standardized Test Vector Leakage Assessment (TVLA) methodology. These Crypto accelerator cores are portable to any FPGA or ASIC technologies.

查看 AES-ECB 1 Billion Trace DPA Resistant Crypto Accelerator 详细介绍:

- 查看 AES-ECB 1 Billion Trace DPA Resistant Crypto Accelerator 完整数据手册

- 联系 AES-ECB 1 Billion Trace DPA Resistant Crypto Accelerator 供应商

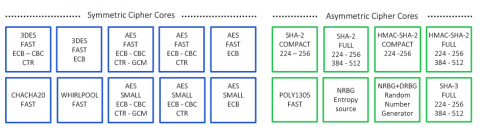

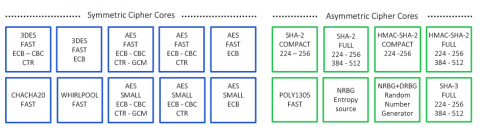

Block Diagram of the AES-ECB 1 Billion Trace DPA Resistant Crypto Accelerator