You are here:

A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell

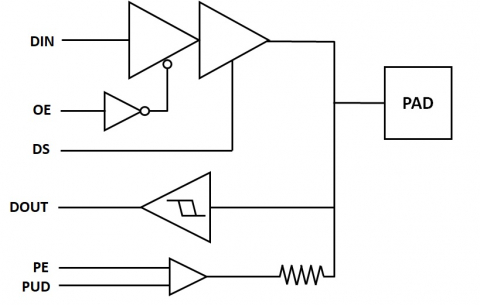

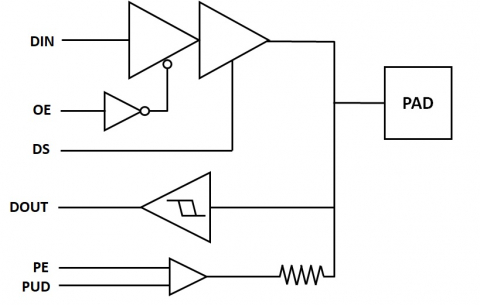

This silicon proven Certus 180 IO library is specifically tailored to address gaps in the native foundry IO offerings for this node. It features a 1.2-1.8V GPIO with selectable dual drive strengths and an optional internal 105KΩ pull-up or pull-down resistor. ESD protection cells for IO and core supplies are constructed in an efficient 60um x 80um footprint. The analog suite includes 1.8V and 5V low-cap analog / RF cells, a 7.5V OTP programming cell, and an ultra-low leakage / low capacitance 20-36V HV analog cell using only baseline CMOS processing layers. The library is enriched with filler, corner, domain break, and secondary CDM cells to allow for flexible segment construction.

Built into our IO libraries and also offered as a separate service is our strong ESD expertise. Certus was founded by ESD engineers, and our results speak for themselves. We consistently exceed the ESD targets of 2KV HBM and 500V CDM and provide on-chip solutions for standards such as IEC-61000-4-2, system-level ESD, and Cable Discharge Events (CDE).

Certus supports IO libraries across multiple nodes, including 180nm, 130nm, 65nm, 40nm, 28nm, 22nm, and 16/12nm. Certus is particularly suited to providing custom variants in a cost-efficient framework. Please contact us for supplementary physical or electrical features that can suit your needs.

Built into our IO libraries and also offered as a separate service is our strong ESD expertise. Certus was founded by ESD engineers, and our results speak for themselves. We consistently exceed the ESD targets of 2KV HBM and 500V CDM and provide on-chip solutions for standards such as IEC-61000-4-2, system-level ESD, and Cable Discharge Events (CDE).

Certus supports IO libraries across multiple nodes, including 180nm, 130nm, 65nm, 40nm, 28nm, 22nm, and 16/12nm. Certus is particularly suited to providing custom variants in a cost-efficient framework. Please contact us for supplementary physical or electrical features that can suit your needs.

查看 A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell 详细介绍:

- 查看 A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell 完整数据手册

- 联系 A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell 供应商

Block Diagram of the A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell

TSMC IP

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL

- Complete USB Type-C Power Delivery PHY, RTL, and Software