Deeply Embedded AI Accelerator for Microcontrollers and End-Point IoT Devices

You are here:

1.8V/3.3V Switchable GPIO With 5V I2C Open Drain & Analog in 16nm

16nm & 12nm Flip-Chip IO library with dynamically switchable 1.8V/3.3V GPIO, 5V I2C / SMBUS open-drain cell, 5V OTP cell, 1.8V & 3.3V analog cells, and associated ESD.

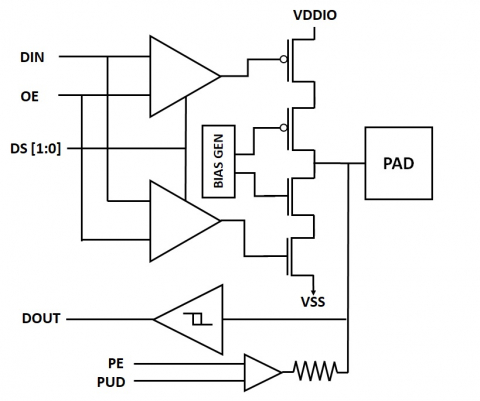

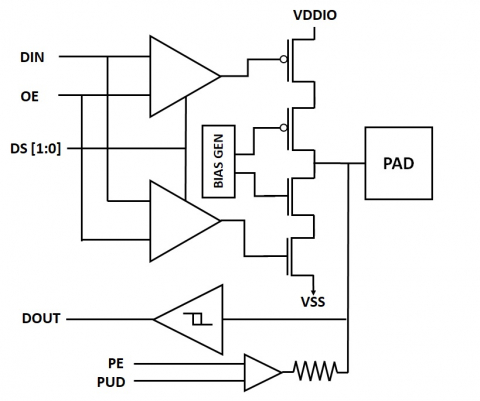

A key attribute of this library is its ability to detect and dynamically adjust to a VDDIO supply of 1.8V or 3.3V during system operation. The GPIO cell can be configured as input, output, open-source, or open-drain with an optional internal 50K ohm pull-up or pull-down resistor. Four selectable drive strengths are offered (25-235MHz @1.8V, 10pF) to optimize across SSO currents & power. The output driver exhibits 50Ω (±20%) termination across PVT to reduce reflections at higher operating frequencies. Supply cells for VDDIO, VREF, and core VDD include necessary built-in ESD circuitry. A 5V I2C / SMBUS open-drain (fail-safe) cell, 5V OTP programming gate cell and 1.8V & 3.3V analog cells with ESD protection are included. The library features protection break cells to allow for separate grounds while maintaining ESD robustness. ESD design targets are 2KV HBM, & 500V CDM, yet this library has consistently demonstrated 4KV HBM. This library can also support 2KV IEC 61000-4-2 system ESD with appropriate integration

A key attribute of this library is its ability to detect and dynamically adjust to a VDDIO supply of 1.8V or 3.3V during system operation. The GPIO cell can be configured as input, output, open-source, or open-drain with an optional internal 50K ohm pull-up or pull-down resistor. Four selectable drive strengths are offered (25-235MHz @1.8V, 10pF) to optimize across SSO currents & power. The output driver exhibits 50Ω (±20%) termination across PVT to reduce reflections at higher operating frequencies. Supply cells for VDDIO, VREF, and core VDD include necessary built-in ESD circuitry. A 5V I2C / SMBUS open-drain (fail-safe) cell, 5V OTP programming gate cell and 1.8V & 3.3V analog cells with ESD protection are included. The library features protection break cells to allow for separate grounds while maintaining ESD robustness. ESD design targets are 2KV HBM, & 500V CDM, yet this library has consistently demonstrated 4KV HBM. This library can also support 2KV IEC 61000-4-2 system ESD with appropriate integration

查看 1.8V/3.3V Switchable GPIO With 5V I2C Open Drain & Analog in 16nm 详细介绍:

- 查看 1.8V/3.3V Switchable GPIO With 5V I2C Open Drain & Analog in 16nm 完整数据手册

- 联系 1.8V/3.3V Switchable GPIO With 5V I2C Open Drain & Analog in 16nm 供应商

Block Diagram of the 1.8V/3.3V Switchable GPIO With 5V I2C Open Drain & Analog in 16nm

TSMC IP

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL

- Complete USB Type-C Power Delivery PHY, RTL, and Software