You are here:

8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications. Approved based on the functional safety assignments of a Safety Element Out-of-Context (SEooC), which includes the ISO 26262 compliant development process and the qualitative approach with respect to hardware safety analysis, D45-SE is certified to be used in safety-related applications such as Millimeter Wave Radar Sensor, Around View Monitor system (AVMS), Vehicle Instrument Cluster, Powertrain DCU, Infotainment DCU, Front/Rear different applications for ZCU.

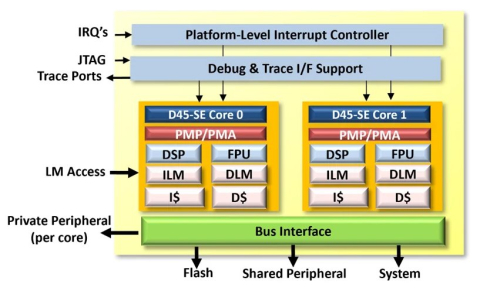

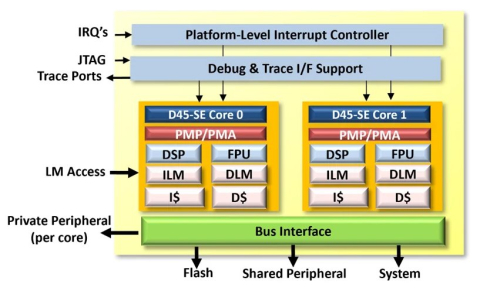

The D45-SE includes “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, “P” Packed-SIMD/DSP instructions, and “B” bit manipulation. D45-SE equipped with comprehensive SIMD/DSP instructions that can boost the performance of voice, audio, image and signal processing. Its ”B” extensions provide some combination of code size reduction, performance improvement, and energy reduction, and “FD” extensions support IEEE754-compliance single and double precision floating point instructions. D45-SE incorporates MemBoost to greatly enhance memory bandwidth and reduce memory latencies for applications with intensive memory accesses. Other features include ECC for memory soft error protection, Platform-Level Interrupt Controller (PLIC) with enhancements for vectored dispatch and priority-based preemption, CoDense™ and StackSafe™ for software quality improvement, PowerBrake and WFI for power management.

The D45-SE includes “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, “P” Packed-SIMD/DSP instructions, and “B” bit manipulation. D45-SE equipped with comprehensive SIMD/DSP instructions that can boost the performance of voice, audio, image and signal processing. Its ”B” extensions provide some combination of code size reduction, performance improvement, and energy reduction, and “FD” extensions support IEEE754-compliance single and double precision floating point instructions. D45-SE incorporates MemBoost to greatly enhance memory bandwidth and reduce memory latencies for applications with intensive memory accesses. Other features include ECC for memory soft error protection, Platform-Level Interrupt Controller (PLIC) with enhancements for vectored dispatch and priority-based preemption, CoDense™ and StackSafe™ for software quality improvement, PowerBrake and WFI for power management.

查看 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications 详细介绍:

- 查看 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications 完整数据手册

- 联系 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications 供应商

Block Diagram of the 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

RISC-V; superscalar;dual-issue;8-stage pipeline;microprocessor;DSP IP

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP (DSP)

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 64-bit RISC-V Multicore Processor with 1024-bit Vector Extension

- Compact, Secure and Performance Efficiency 32-bit RISC-V Core

- 32 bit RISC-V Multicore Processor with 256-bit VLEN and AMM