You are here:

7-bit, 64 GSPS ADC Ultra Low Power

The ODT-ADS-7B64G-3 is an ultra-high-bandwidth time-interleaved ADC designed in a 3nm CMOS process.

This 7-bit, 64GSPS ADC supports ac-coupled input signals up to Nyquist and features a full-scale range of 0.45Vpp differential, excellent dynamic performance, and low noise operation.

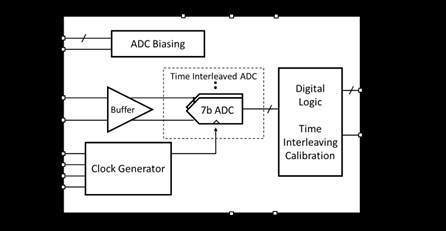

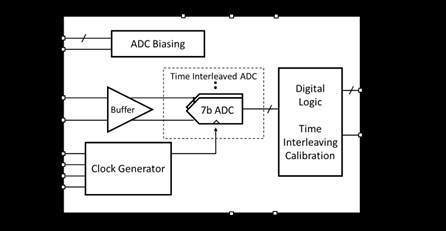

The ADC architecture is optimized to maximize performance while minimizing power and area consumption. The ac-coupled RF input is internally buffered and sampled and then distributed efficiently to time-interleaved ADC channels.

The ADC includes built in calibration to remove time interleaving artifacts, including offset mismatch, gain mismatch and timing skew. It also includes internal analog test probes to enable measurement of DC signals.

To maximize SNR, the ADC includes an ultra-low-jitter clock distribution network.

This 7-bit, 64GSPS ADC supports ac-coupled input signals up to Nyquist and features a full-scale range of 0.45Vpp differential, excellent dynamic performance, and low noise operation.

The ADC architecture is optimized to maximize performance while minimizing power and area consumption. The ac-coupled RF input is internally buffered and sampled and then distributed efficiently to time-interleaved ADC channels.

The ADC includes built in calibration to remove time interleaving artifacts, including offset mismatch, gain mismatch and timing skew. It also includes internal analog test probes to enable measurement of DC signals.

To maximize SNR, the ADC includes an ultra-low-jitter clock distribution network.

查看 7-bit, 64 GSPS ADC Ultra Low Power 详细介绍:

- 查看 7-bit, 64 GSPS ADC Ultra Low Power 完整数据手册

- 联系 7-bit, 64 GSPS ADC Ultra Low Power 供应商

Block Diagram of the 7-bit, 64 GSPS ADC Ultra Low Power

Analog & Mixed Signal A2D Converter IP

- Analog Front End: 2x 12-bit 4 GSPS IQ ADCs, 2x 12-bit 8GSPS IQ DACs, bandgap, temp sensor, PLL, 4 x LDO

- Analog Front End: 8x 12-bit 2 GSPSADCs, 4x 12-bit 200 MSPS ADCs, TVM, PLL, LDO

- Analog Front End: 16x 12-bit 200 MSPS ADCs, 14x Voltage DACs, 4x 250 MSPS DACs, 4x TVM, LDO

- Analog Front End: 8x 9-bit, 1 GSPS ADCs, PLL

- Analog Front End: 4 channels of 12-bit 2 GSPS ADC IQ Pairs, 4 channels of 12-bit 2 GSPS DAC IQ Pairs, PVT & Integrated PLL

- Analog Front End: 1 channel of 12-bit 2 GSPS ADC IQ Pairs, 1 channel of 12-bit 2 GSPS DAC IQ Pairs, PVT & Integrated PLL