You are here:

6b 3.5GS/s high-speed DAC

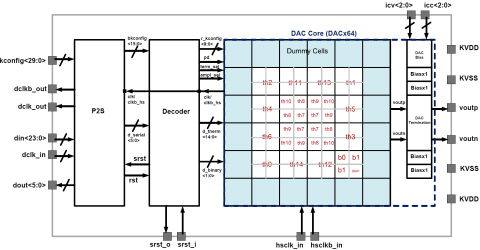

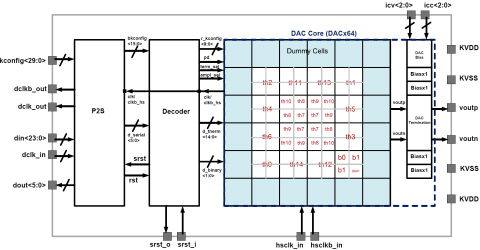

STAR3010 is a high-speed DAC for RF applications. The DAC is used in a wireless application with I/Q channels. It uses a 4-2 segmented architecture to provide a good trade-off between dynamic performance and array size. The input to the DAC is a stream of 24bits at 880MHz from a digital macro, running at a quarter of the DAC sampling rate. As such, the P2S block handles the data timing interface between analog and the digital block, as well as serializing the parallel digital data into a series 3.52Gbps datastream. As a test and debug feature of the P2S, the data is de-serialized, and fed back to the digital block for bit-error-rate checking. The DAC array consists of randomized current-steering DAC unit cells.

The DAC achieves an SFDR of 36dB and an SNDR of 32dB up to the nyquist bandwidth of 1.76GHz. For a sine-wave output frequency of 1.14GHz, and a full-scale amplitude of 550mVppd, the power consumption of the is 101mW.

The DAC achieves an SFDR of 36dB and an SNDR of 32dB up to the nyquist bandwidth of 1.76GHz. For a sine-wave output frequency of 1.14GHz, and a full-scale amplitude of 550mVppd, the power consumption of the is 101mW.

查看 6b 3.5GS/s high-speed DAC 详细介绍:

- 查看 6b 3.5GS/s high-speed DAC 完整数据手册

- 联系 6b 3.5GS/s high-speed DAC 供应商

Block Diagram of the 6b 3.5GS/s high-speed DAC