50mA CMOS buck regulator

Two pins are required for this function: 5V input and 1.8V return. An external 50uH inductor and 1µ F capacitor are required.

Designed for TSMC 0.18µ processes with 5V fet option.

查看 50mA CMOS buck regulator 详细介绍:

- 查看 50mA CMOS buck regulator 完整数据手册

- 联系 50mA CMOS buck regulator 供应商

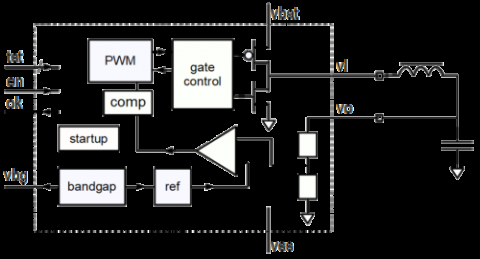

Block Diagram of the 50mA CMOS buck regulator

buck regulator IP

- DC/DC Buck Regulator

- Low-BoM, inductor-based buck switching regulator with high efficiency, full PWM mode

- Low-BoM, inductor-based buck switching regulator with high efficiency, full PWM mode design in TSMC 40 ULP

- Buck Switching Inductor Regulator - High temperature (Grade 1, Tj=150�)

- Buck Switching Inductor Regulator - High temperature (Grade 1, Tj=150�)

- Buck Switching Inductor Regulator - High temperature (Grade 1, Tj=150�)