You are here:

40nm 1.1V 16MHz-2GHz Fractional-N Clock-PLL

The TRV301TSM40LP IP is a 1.1V low-power low-silicon-area 16MHz-to-2GHz Fractional-N Clock PLL implemented in TSMC Low-Power 40nm CMOS process technology. Its low loop filter bandwidth and low-frequency reference clock makes it especially suitable for use in clock synthesis for DAC, ADC and digital subsystems within wireless communication and broadcast integrated circuit chipsets (LTE, WiFi, WiMAX, DAB, DAB+, FM, HDFM, DRM, etc).

查看 40nm 1.1V 16MHz-2GHz Fractional-N Clock-PLL 详细介绍:

- 查看 40nm 1.1V 16MHz-2GHz Fractional-N Clock-PLL 完整数据手册

- 联系 40nm 1.1V 16MHz-2GHz Fractional-N Clock-PLL 供应商

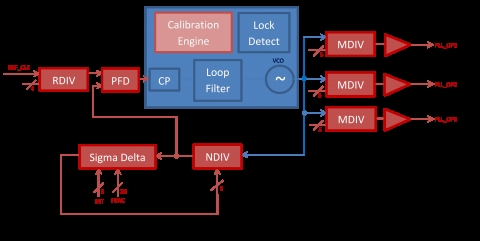

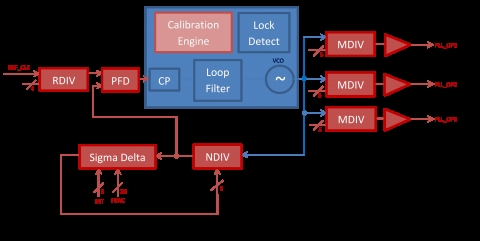

Block Diagram of the 40nm 1.1V 16MHz-2GHz Fractional-N Clock-PLL

Clock PLL 40nm Low Power Low Area IP

- Low Power Clock Multiplier PLL for 40nm TSMC ULP CMOS

- UniPHY™ IoT IP: Ultra Low Power and Smallest PHY area for low cost Chiplets

- 1-10G Low Power SERDES - TSMC 40G

- Low Power PCIe3 SERDES PHY - TSMC 40G

- Low Voltage, Low Power Fractional-N PLLs

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL