Secure-IC's Securyzr™ Fully Digital Physically Unclonable Function (PUF) - PQC Ready

You are here:

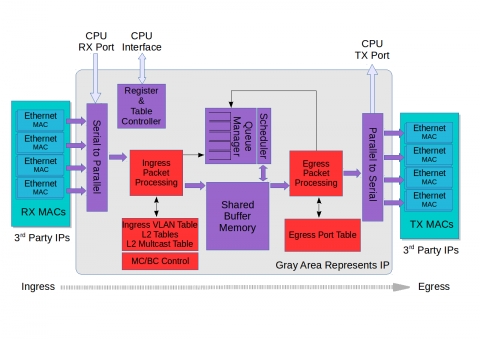

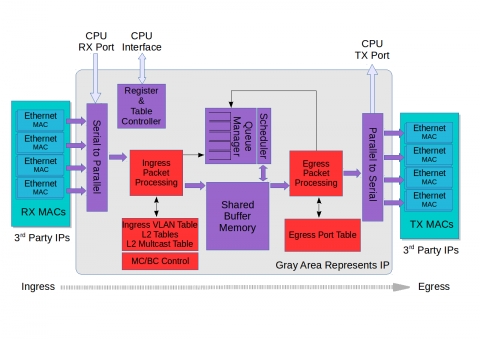

320Gbps Ethernet Switch

Packet Architects offers a series of high speed switching IPs which are developed using the unique FlexSwitch toolchain. The toolchain allows a fast and flexible development of switching/routing IP for any packet based technology.

This L2 Ethernet Switching IP offers a full range of features with full wirespeed on all ports plus a high speed CPU port. Each port has priority queues which are controlled by a strict priority scheduler allowing the most timing critical packets to get minimal delay while providing a fairness between queues. The switching core is built around a shared buffer memory architecture allowing head of line blocking free switching on all ports operating at wirespeed. It offers dynamic per port and per priority usage of the packet buffer memory along with buffer limiters to limit how much an egress port / priority uses of total buffer memory. The switching core also features multiple VLAN tagging and untagging along with egress VLAN translation.

The L2 Ethernet Switching IP features a processor interface allowing setup of tables and register. It also features a packet based CPU port which can be used to both send and receive ethernet frames to/from the switching IP.

This IP requires no software setup to be used, it is ready to receive and forward Ethernet frames once downloaded to FPGA and connected to MACs. It has hardware learning for MAC addresses.

This L2 Ethernet Switching IP offers a full range of features with full wirespeed on all ports plus a high speed CPU port. Each port has priority queues which are controlled by a strict priority scheduler allowing the most timing critical packets to get minimal delay while providing a fairness between queues. The switching core is built around a shared buffer memory architecture allowing head of line blocking free switching on all ports operating at wirespeed. It offers dynamic per port and per priority usage of the packet buffer memory along with buffer limiters to limit how much an egress port / priority uses of total buffer memory. The switching core also features multiple VLAN tagging and untagging along with egress VLAN translation.

The L2 Ethernet Switching IP features a processor interface allowing setup of tables and register. It also features a packet based CPU port which can be used to both send and receive ethernet frames to/from the switching IP.

This IP requires no software setup to be used, it is ready to receive and forward Ethernet frames once downloaded to FPGA and connected to MACs. It has hardware learning for MAC addresses.

查看 320Gbps Ethernet Switch 详细介绍:

- 查看 320Gbps Ethernet Switch 完整数据手册

- 联系 320Gbps Ethernet Switch 供应商

Block Diagram of the 320Gbps Ethernet Switch

ethernet IP

- 10G-100G MACsec Security Module for Ethernet

- 224G Ethernet PHY in TSMC (N3E, N2P)

- 112G Ethernet PHY in TSMC (N7, N6, N5, N3P)

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency