You are here:

32-bit RISC-V CPU with M, Zicsr extensions, and External Debug support

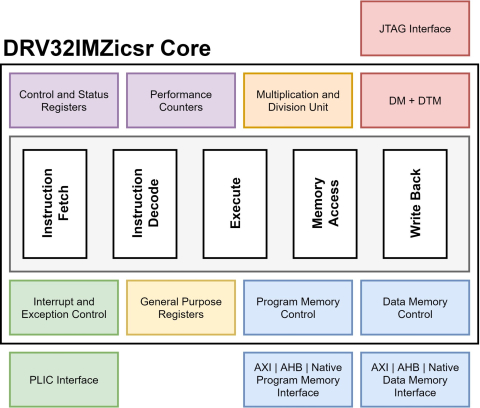

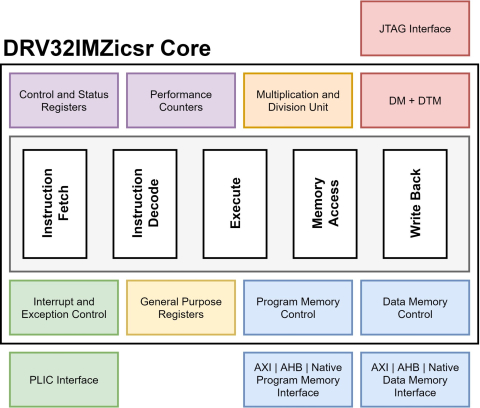

The Core belongs to the latest DCD’s DRVX Core Family, with:

* a five-stage pipeline,

* Harvard architecture

* flexible size of program and data memory together with their allocation in address space.

It is possible to select CPU interface as:

* AXI,

* AHB,

* Native.

The DRV32IMZicsr was developed as ISO26262 Safety Element out of Context (SEooC) and is technology independent, and compatible with all FPGA and ASIC vendors.

The DRV32IMZicsr can be used along with a wide range of DCD’s peripherals, like e.g. DMA, SPI, UART, PWM, CAN etc. This holistic approach makes the DRV32IMZicsr core a good choice for application for e.g. Automotive, Internet of Things, Embedded, Consumer Electronics, and more.

The DRV32IMZicsr is a 32-bit core with 32 General Purpose Registers. It performs arithmetic and logic instructions, loads, stores, conditional branches, and unconditional jumps. The proper usage of base instructions provides an additional set of pseudo instructions which are available in the RISC-V assembly language. The M extension enables the use of additional integer multiplication and division instructions due to Multiplication and Division unit, which is responsible for handling these instructions. The Zicsr extension provides the means to access Control and Status Registers, which in turn enables interrupt and exception handling according to version 20211203 of The RISC-V Instruction Set Manual Volume II: Privileged Architecture. With Zicsr extension DRV32IMZicsr core is also equipped with performance counters and timers. External Debug support utilizes JTAG debug interface and is implemented with conformance to the RISC-V Debug Specification 0.13.2 and 1.0.0. That allows core debugging with all the tools compatible with this specification available on the market.

The DRV32IMZicsr core is delivered with a fully automated test bench and a complete set of tests, allowing easy package validation at each stage of the SoC design flow.

* a five-stage pipeline,

* Harvard architecture

* flexible size of program and data memory together with their allocation in address space.

It is possible to select CPU interface as:

* AXI,

* AHB,

* Native.

The DRV32IMZicsr was developed as ISO26262 Safety Element out of Context (SEooC) and is technology independent, and compatible with all FPGA and ASIC vendors.

The DRV32IMZicsr can be used along with a wide range of DCD’s peripherals, like e.g. DMA, SPI, UART, PWM, CAN etc. This holistic approach makes the DRV32IMZicsr core a good choice for application for e.g. Automotive, Internet of Things, Embedded, Consumer Electronics, and more.

The DRV32IMZicsr is a 32-bit core with 32 General Purpose Registers. It performs arithmetic and logic instructions, loads, stores, conditional branches, and unconditional jumps. The proper usage of base instructions provides an additional set of pseudo instructions which are available in the RISC-V assembly language. The M extension enables the use of additional integer multiplication and division instructions due to Multiplication and Division unit, which is responsible for handling these instructions. The Zicsr extension provides the means to access Control and Status Registers, which in turn enables interrupt and exception handling according to version 20211203 of The RISC-V Instruction Set Manual Volume II: Privileged Architecture. With Zicsr extension DRV32IMZicsr core is also equipped with performance counters and timers. External Debug support utilizes JTAG debug interface and is implemented with conformance to the RISC-V Debug Specification 0.13.2 and 1.0.0. That allows core debugging with all the tools compatible with this specification available on the market.

The DRV32IMZicsr core is delivered with a fully automated test bench and a complete set of tests, allowing easy package validation at each stage of the SoC design flow.

查看 32-bit RISC-V CPU with M, Zicsr extensions, and External Debug support 详细介绍:

- 查看 32-bit RISC-V CPU with M, Zicsr extensions, and External Debug support 完整数据手册

- 联系 32-bit RISC-V CPU with M, Zicsr extensions, and External Debug support 供应商

Block Diagram of the 32-bit RISC-V CPU with M, Zicsr extensions, and External Debug support

RISC-V IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- 32-bit Embedded RISC-V Functional Safety Processor