You are here:

32-bit High Performance Single/Multicore RISC System-on-Chip

The CC100-S is a synthesisable Verilog model of a high performance 32-bit RISC processor based System-on-Chip. The model is highly configurable and embeds a wide range of peripherals. The SoC can be efficiently implemented on FPGA and ASIC technologies and uses standard synchronous memory cells for caches and register file.

查看 32-bit High Performance Single/Multicore RISC System-on-Chip 详细介绍:

- 查看 32-bit High Performance Single/Multicore RISC System-on-Chip 完整数据手册

- 联系 32-bit High Performance Single/Multicore RISC System-on-Chip 供应商

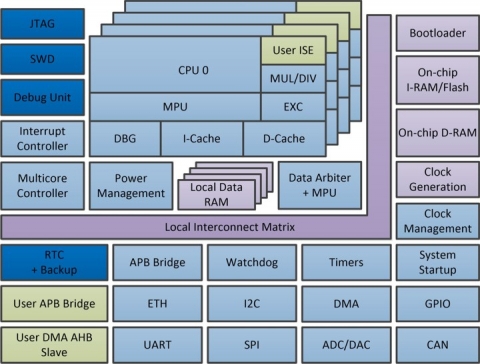

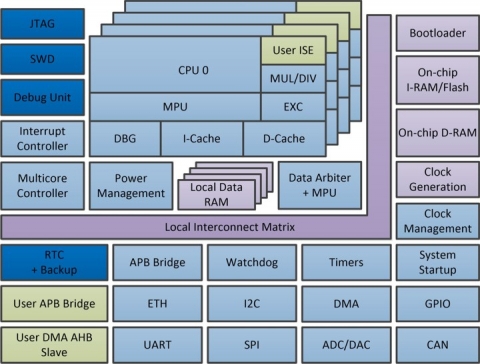

Block Diagram of the 32-bit High Performance Single/Multicore RISC System-on-Chip

SoC IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Tessent SoC debug and optimization

- Compute Express Link (CXL) 2.0 Controller with AMBA AXI interface

- Root of Trust eSecure module for SoC security

- Magillem Connectivity System Integration Automation

- Secure-IC's Securyzr™ 1.5Tbps MACsec Engine