You are here:

32位,5流水线级,单发射,为功能安全设计的嵌入式处理器核

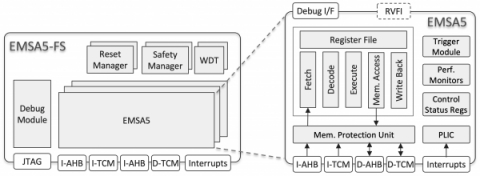

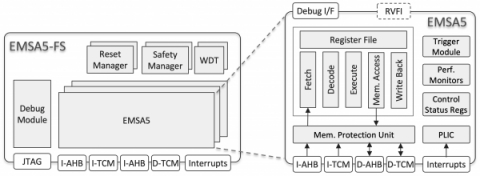

EMSA5-FS是一个为功能安全而设计的处理器核。容错处理器使用EMSA5的双实例或三实例,EMSA5是一种实现RISC-V指令集体系结构(ISA)的高效32位嵌入式处理器IP核。

哈佛体系结构EMSA5处理器按顺序实现单发射,顺序执行的5级流水线,支持RISC-V 32位base integer指令集(RV32I)或32位base embedded指令集(RV32E)。EMSA5可以支持机器和用户特权模式,也可以选择标准乘法(M)、压缩(C)、控制和状态寄存器(Zicsr)和指令围栏(Zifencei)RISC-V扩展。处理器核通过两个32位AHB lite总线(一个用于数据,一个用于指令)及其中断线与系统通信。

为满足最严格的功能安全要求而设计,EMSA5-FS实现了一个内存保护单元,采用模块冗余,使用纠错码(ECC),并提供了样本重置和安全管理器模块。特权操作模式提供了一种机制,可以将应用程序用户模式进程彼此隔离,并将其与以计算机模式运行的受信任代码隔离。高度可配置的内存保护单元支持内存分区,它通过限制对内存和内存映射模块(例如外围设备)的访问或特定类型的访问来提供保护。ECC保护存储器和总线,模块冗余保护内部处理器模块。最后,safety manager提供逻辑和时序监控,可以定制以满足最终应用程序的需求。

作为CAST处理器内核系列的一部分,EMSA5-FS处理器内核的设计易于重用,经过严格验证,并附带ISO 26262 ASIL-D Ready证书。

哈佛体系结构EMSA5处理器按顺序实现单发射,顺序执行的5级流水线,支持RISC-V 32位base integer指令集(RV32I)或32位base embedded指令集(RV32E)。EMSA5可以支持机器和用户特权模式,也可以选择标准乘法(M)、压缩(C)、控制和状态寄存器(Zicsr)和指令围栏(Zifencei)RISC-V扩展。处理器核通过两个32位AHB lite总线(一个用于数据,一个用于指令)及其中断线与系统通信。

为满足最严格的功能安全要求而设计,EMSA5-FS实现了一个内存保护单元,采用模块冗余,使用纠错码(ECC),并提供了样本重置和安全管理器模块。特权操作模式提供了一种机制,可以将应用程序用户模式进程彼此隔离,并将其与以计算机模式运行的受信任代码隔离。高度可配置的内存保护单元支持内存分区,它通过限制对内存和内存映射模块(例如外围设备)的访问或特定类型的访问来提供保护。ECC保护存储器和总线,模块冗余保护内部处理器模块。最后,safety manager提供逻辑和时序监控,可以定制以满足最终应用程序的需求。

作为CAST处理器内核系列的一部分,EMSA5-FS处理器内核的设计易于重用,经过严格验证,并附带ISO 26262 ASIL-D Ready证书。

查看 32位,5流水线级,单发射,为功能安全设计的嵌入式处理器核 详细介绍:

- 查看 32位,5流水线级,单发射,为功能安全设计的嵌入式处理器核 完整数据手册

- 联系 32位,5流水线级,单发射,为功能安全设计的嵌入式处理器核 供应商

Block Diagram of the 32位,5流水线级,单发射,为功能安全设计的嵌入式处理器核

32-bit Processor IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- InCore Calcite Series: 32b/64b RISC-V 5-stage, scalar, in-order, Application Processor. Linux and multi-core capable. Maps upto ARM A-35. Optimal PPA.