You are here:

32-bit 8-stage superscalar processor that supports RISC-V specification, including GCN

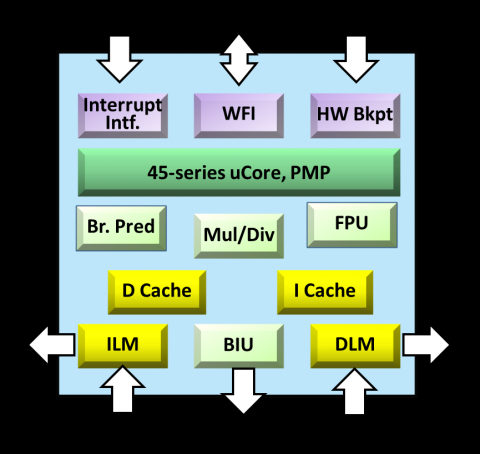

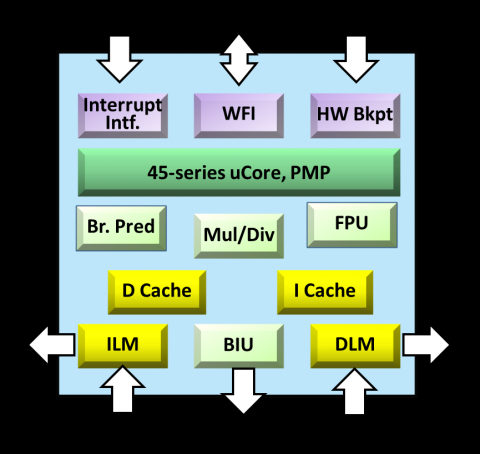

The 32-bit N45 is an 8-stage superscalar processor that supports RISC-V specification, including “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, and “N” for user-level interrupts. It issues two instructions per cycle that significantly increases the performance efficiency that is important for many applications. Its “FD” extensions support IEEE754-compliance single and double precision floating point instructions as well. It incorporates MemBoost to greatly enhance memory bandwidth and reduce memory latencies for applications with intensive memory accesses. In addition, N45 features advanced low power branch prediction mechanism for efficient branch execution, instruction and data caches, local memories, and ECC error protection. It also includes vectored and preemptive interrupt controller to serve diversified system events, AXI 64-bit bus, rich power management, and JTAG debug and trace interface for software development support.

查看 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCN 详细介绍:

- 查看 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCN 完整数据手册

- 联系 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCN 供应商

Block Diagram of the 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCN

RISC-V; superscalar;dual-issue;8-stage pipeline;microprocessor; IP

- Superscalar Out-of-Order Execution Multicore Cluster

- 64-Bit 8-stage superscalar processor that supports RISC-V specification, including GCN

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP (DSP)

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications