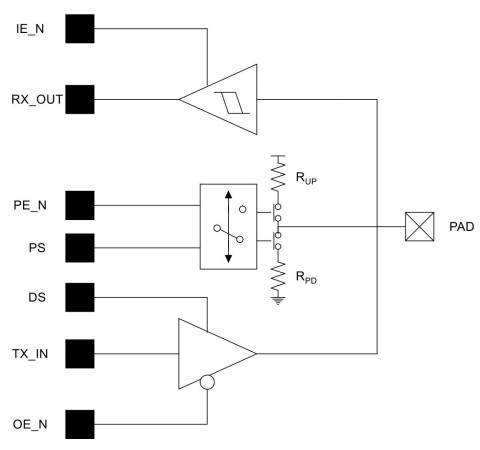

3.3V general purpose I/O for 28nm CMOS

Supported features include core isolation, output enable and pull enable. Extra features such as input enable/disable, programmable drive strength and pull select, can be supported upon request.

By default, a 2kV HBM ESD protection is included. This is however easily scaled to any desired level.

This specific IP macro is designed in TSMC 28nm RF HPC+ MMWave, and can be ported to other technologies upon request using Sofics inhouse design tool flow.

查看 3.3V general purpose I/O for 28nm CMOS 详细介绍:

- 查看 3.3V general purpose I/O for 28nm CMOS 完整数据手册

- 联系 3.3V general purpose I/O for 28nm CMOS 供应商

Block Diagram of the 3.3V general purpose I/O for 28nm CMOS