You are here:

3.25 Gigabit SerDes

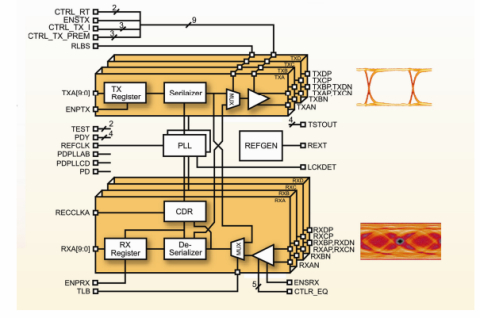

The MXL-SRDS-3204 is a Quad Gigabit SerDes implemented in digital CMOS technology. Each of the four channels supports data rate up to 3.2Gbps. It is compatible with router-backplane links, PCI Express, 10 Gbps Ethernet (XAUI), Fibre Channel, SFI-5, SPI-5, Infiniband, and other communication applications. The frequency synthesizing PLL is fully integrated including the loop filter, and has a programmable multiplication factor (4, 5, 8, 10, 16, and 20). Each transmitter accepts an 8 or 10-bit parallel data, serializes it, and outputs the serial data differentially. Each receiver accepts serial differential data at up to 3.2Gbps, recovers the clock and data, de-serializes the data, and makes the data available at the parallel bus.

查看 3.25 Gigabit SerDes 详细介绍:

- 查看 3.25 Gigabit SerDes 完整数据手册

- 联系 3.25 Gigabit SerDes 供应商

Block Diagram of the 3.25 Gigabit SerDes

SERDES IP

- PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Low-Latency SerDes PMA - 10GbE, 25GbE

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- 400G ultra low latency 56/112G FEC and SERDES IP sub 10ns latency

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency