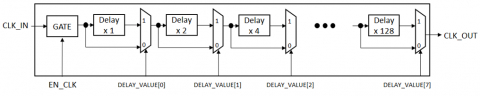

256-steps adjustable delay cell

查看 256-steps adjustable delay cell 详细介绍:

- 查看 256-steps adjustable delay cell 完整数据手册

- 联系 256-steps adjustable delay cell 供应商

Block Diagram of the 256-steps adjustable delay cell

delay cell IP

- Rising edge delay cell for control circuits, 10ns - TSMC 180nm

- Rising edge delay cell for control circuits, 20ns - TSMC 180nm

- Rising edge delay cell for control circuits, 40ns - TSMC 180nm

- TON delay cell for hysteretic mode function - TSMC 180nm

- DLL-based cell that generates 32 phase delay for FTSDC021; UMC 0.11um HS/AE (AL Advanced Enhancement) Logic Process

- DLL-based cell that generates 32 phase delay for SDIO; Frequency range: 52MHz~208MHz; UMC 28nm HPC Logic Process