You are here:

2-stage pipeline RISC-V processor core

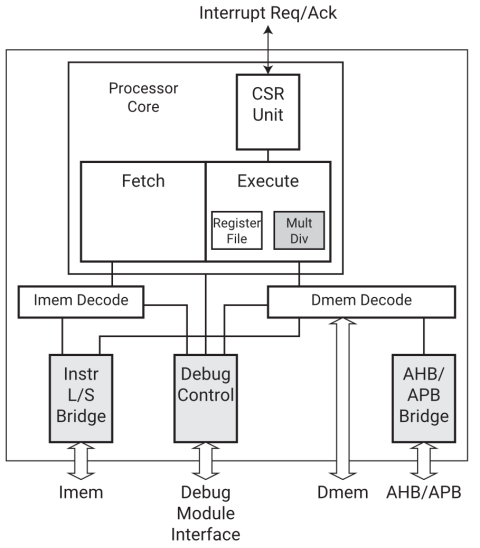

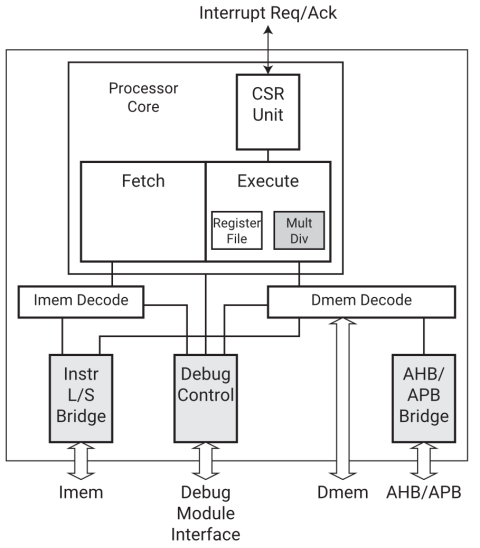

IQonIC Works RV32EC_P2 Core is a 2-stage pipeline RISC-V processor core, designed to meet the needs of small, low-power embedded applications, running only trusted firmware.

The processor interfaces to separate compiled memory blocks for code and data memories, and to memory mapped I/O blocks connected to Advanced High-Performance Bus (AHB) and Advanced Peripheral Bus (APB) buses. A clock control block gates clocks to the core depending on the operating mode.

The processor interfaces to separate compiled memory blocks for code and data memories, and to memory mapped I/O blocks connected to Advanced High-Performance Bus (AHB) and Advanced Peripheral Bus (APB) buses. A clock control block gates clocks to the core depending on the operating mode.

查看 2-stage pipeline RISC-V processor core 详细介绍:

- 查看 2-stage pipeline RISC-V processor core 完整数据手册

- 联系 2-stage pipeline RISC-V processor core 供应商

Block Diagram of the 2-stage pipeline RISC-V processor core

RISC-V processor core IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- 32-bit Embedded RISC-V Functional Safety Processor