Secure-IC's Securyzr Crypto Coprocessor with integrated Post-Quantum Cryptography IPs

You are here:

2.5Gbps以太网MAC IP核

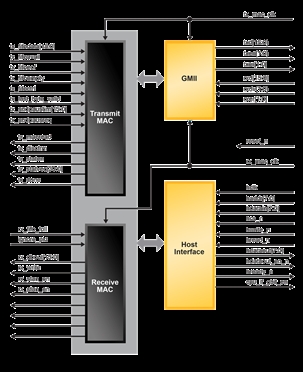

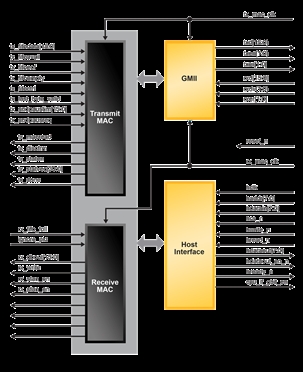

2.5GMAC IP核支持主机处理器和以太网网络之间的数据传输和接收。以太网MAC的主要功能是确保在通过以太网传输数据帧时满足802.3 IEEE标准中规定的媒体访问规则。在接收端,以太网MAC提取帧中的不同部分,并将它们通过FIFO接口传输到更高的应用层。

2.5GMAC IP核实现了在客户端应用和以太网网络之间的数据传输和接收。以太网MAC的主要功能是确保在发送和接收以太网数据帧时满足802.3 IEEE标准中规定的媒体访问规则。

在接收端,以太网MAC提取帧数据的不同的部分并将它们通过客户端FIFO接口传输到上一层应用层。从GMII接口接收到的数据首先被缓冲,直到有有效的数据可以通过接收MAC(RX MAC)处理。

然后从输入帧中提取前导码(Preamble)和帧开始符(SFD)信息,以确定一个有效的帧开始传入。接收MAC检查收到的数据包的地址并验证是否可以在传输到FIFO之前接收帧数据。仅将有效的帧传输到FIFO(丢弃欠幅脉冲和碎片)。RX MAC还为每一个数据包提供了统计向量,可以供应用层使用。2.5GMAC IP核通常通过计算CRC来检查是否收到无差错的帧。

在发送端,TX MAC负责物理介质的访问控制。Tx MAC从外部客户端Tx FIFO中读取数据,转换数据格式为一个以太网数据包,并把它传递给GMII模块。

当客户端显示数据包可用并且Tx MAC在适当的状态时,Tx MAC从Tx客户端FIFO读取数据。TX MAC预修复数据的前导码和帧开始符信息,并在数据最后添加帧校验序列。

2.5GMAC IP核实现了在客户端应用和以太网网络之间的数据传输和接收。以太网MAC的主要功能是确保在发送和接收以太网数据帧时满足802.3 IEEE标准中规定的媒体访问规则。

在接收端,以太网MAC提取帧数据的不同的部分并将它们通过客户端FIFO接口传输到上一层应用层。从GMII接口接收到的数据首先被缓冲,直到有有效的数据可以通过接收MAC(RX MAC)处理。

然后从输入帧中提取前导码(Preamble)和帧开始符(SFD)信息,以确定一个有效的帧开始传入。接收MAC检查收到的数据包的地址并验证是否可以在传输到FIFO之前接收帧数据。仅将有效的帧传输到FIFO(丢弃欠幅脉冲和碎片)。RX MAC还为每一个数据包提供了统计向量,可以供应用层使用。2.5GMAC IP核通常通过计算CRC来检查是否收到无差错的帧。

在发送端,TX MAC负责物理介质的访问控制。Tx MAC从外部客户端Tx FIFO中读取数据,转换数据格式为一个以太网数据包,并把它传递给GMII模块。

当客户端显示数据包可用并且Tx MAC在适当的状态时,Tx MAC从Tx客户端FIFO读取数据。TX MAC预修复数据的前导码和帧开始符信息,并在数据最后添加帧校验序列。

查看 2.5Gbps以太网MAC IP核 详细介绍:

- 查看 2.5Gbps以太网MAC IP核 完整数据手册

- 联系 2.5Gbps以太网MAC IP核 供应商

Block Diagram of the 2.5Gbps以太网MAC IP核

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software