You are here:

2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe

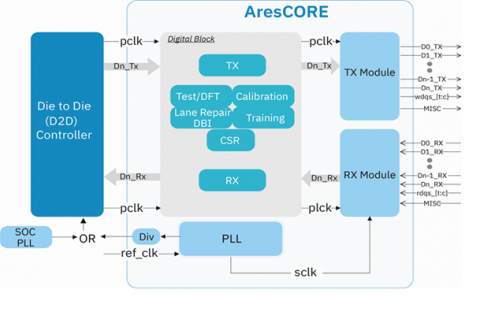

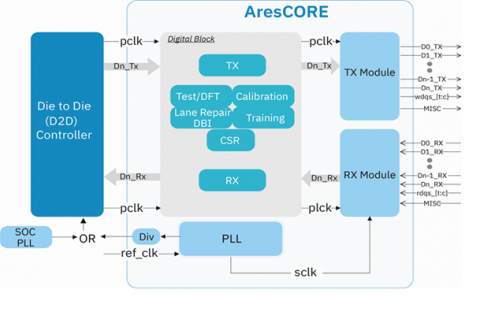

The AresCORE 16G Die-to-Die (D2D) IP implements a wide-parallel and clock forwarded PHY interface for multichannel interconnections up to 16Gbps. The PHY IP is configurable to support the leading standards in the industry such as BOW (Bunch of Wire), and OHBI (Open High Bandwidth Interface) and UCIe (Universal Chiplet Interconnect Express) providing customers a D2D solution that is compliant with industry standards.

AresCORE16 can be configured to support advanced packaging such as CoWoS (Chip-on-Wafer-on-Substrate), InFO (Integrated-Fan-Out) for maximum density, and Organic Substrates for most cost-effective solution covering all market segments.

AresCORE16 can be configured to support advanced packaging such as CoWoS (Chip-on-Wafer-on-Substrate), InFO (Integrated-Fan-Out) for maximum density, and Organic Substrates for most cost-effective solution covering all market segments.

查看 2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe 详细介绍:

- 查看 2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe 完整数据手册

- 联系 2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe 供应商

Block Diagram of the 2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe

SerDes IP

- PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Low-Latency SerDes PMA - 10GbE, 25GbE

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- 400G ultra low latency 56/112G FEC and SERDES IP sub 10ns latency

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency