You are here:

1G/10G TCP/IP Hardware Stack

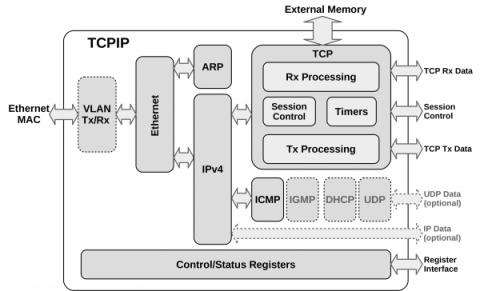

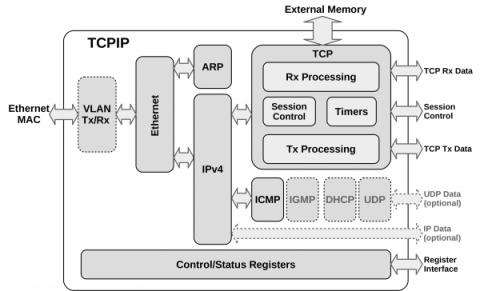

The TCPIP-1G/10G core implements a complete TCP/IP Hardware Protocol Stack. More capable than many offloading engines, it allows systems to connect to an Internet Protocol (IP) network and exchange data using the TCP protocol without requiring assistance from — or even the presence of — a system processor.

The core acts either as a server or a client and without any assistance from the host autonomously system, opens, maintains, and closes TCP connections. The system integrating the TCPIP-1G/10G core can configure network parameters and preferences by accessing its control registers, and the core is then able to receive and send data via streaming data interfaces.

The highly configurable core can adapt to different applications and diverse system requirements. The maximum number of simultaneous TCP sessions is configurable at synthesis time; it can be as high as 32,768 for devices like data servers, or as small as 1 for edge devices requiring minimum silicon area and power. Further user options include implementing a DHCP client that allows the core to automatically be assigned an IP address, enabling or disabling support the reassembly of out-of-order TCP packets data, and integrating a UDP hardware stack with multicast support (IGMPv3). Finally, users can choose the packet processing mode, either cut-through or store-and-forward. In cut-through mode, the payload data are delivered to the host system as they arrive without any internal packet buffering and before the packets’ integrity can be validated. As a result, the core operating in cut-through mode features extremely low latency and requires less memory, but it cannot reassemble out-of-order packets and may deliver data that will subsequently be marked as corrupted. Under the store-and-forward mode of operation, the core will always deliver verified, in-order packets but it will have higher latency and require more memory resources.

The TCPIP-1G/10G core is rigorously verified and available in RTL source or as a targeted FPGA netlist. Its deliverables include a testbench, synthesis and simulation scripts, and comprehensive user documentation.

The core acts either as a server or a client and without any assistance from the host autonomously system, opens, maintains, and closes TCP connections. The system integrating the TCPIP-1G/10G core can configure network parameters and preferences by accessing its control registers, and the core is then able to receive and send data via streaming data interfaces.

The highly configurable core can adapt to different applications and diverse system requirements. The maximum number of simultaneous TCP sessions is configurable at synthesis time; it can be as high as 32,768 for devices like data servers, or as small as 1 for edge devices requiring minimum silicon area and power. Further user options include implementing a DHCP client that allows the core to automatically be assigned an IP address, enabling or disabling support the reassembly of out-of-order TCP packets data, and integrating a UDP hardware stack with multicast support (IGMPv3). Finally, users can choose the packet processing mode, either cut-through or store-and-forward. In cut-through mode, the payload data are delivered to the host system as they arrive without any internal packet buffering and before the packets’ integrity can be validated. As a result, the core operating in cut-through mode features extremely low latency and requires less memory, but it cannot reassemble out-of-order packets and may deliver data that will subsequently be marked as corrupted. Under the store-and-forward mode of operation, the core will always deliver verified, in-order packets but it will have higher latency and require more memory resources.

The TCPIP-1G/10G core is rigorously verified and available in RTL source or as a targeted FPGA netlist. Its deliverables include a testbench, synthesis and simulation scripts, and comprehensive user documentation.

查看 1G/10G TCP/IP Hardware Stack 详细介绍:

- 查看 1G/10G TCP/IP Hardware Stack 完整数据手册

- 联系 1G/10G TCP/IP Hardware Stack 供应商

Block Diagram of the 1G/10G TCP/IP Hardware Stack

TCP/IP Hardware Stack IP

- 40G/50G UDP/IP Hardware Protocol Stack

- 100G UDP/IP Hardware Protocol Stack

- UDP/IP Hardware Protocol Stack

- 10G/25G UDP/IP Hardware Protocol Stack

- RTP / UDP / IP Hardware Stack for Raw, Uncompressed RGB/YUV Video Streams

- RTP / UDP / IP Hardware Stack for H.264/H.265 NAL Video Streams Packet Processing