You are here:

15 Bit 8 kS/s Sigma-Delta ADC

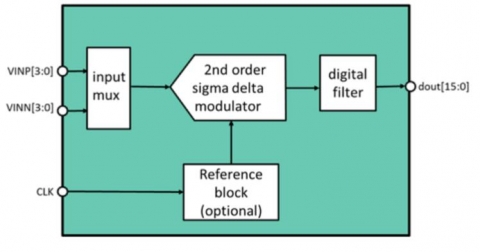

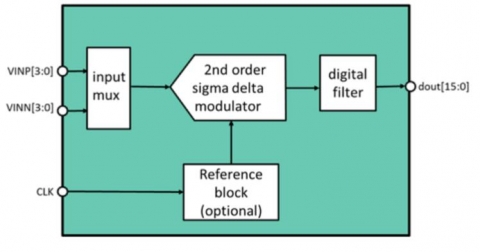

The ADC IP is a general-purpose sigma-delta converter and it is configurable for conversion speed and power consumption with adaptable oversampling ratio.

It is built using typical second order architecture using correlated-double-sampling method. The target application is sampling of transient input voltages with 8kS/s with low-power and 192kS/s respectively.

The ADC IP includes reference voltage generation (optional) and 4-to-1 input multiplexer (optional) providing 4 differential input channels.

The ADC is silicon proven in Automotive mass production using the XFAB XH018 process.

Measurement results and samples are available.

Fraunhofer IIS provides a detailed documentation and support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

It is built using typical second order architecture using correlated-double-sampling method. The target application is sampling of transient input voltages with 8kS/s with low-power and 192kS/s respectively.

The ADC IP includes reference voltage generation (optional) and 4-to-1 input multiplexer (optional) providing 4 differential input channels.

The ADC is silicon proven in Automotive mass production using the XFAB XH018 process.

Measurement results and samples are available.

Fraunhofer IIS provides a detailed documentation and support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

查看 15 Bit 8 kS/s Sigma-Delta ADC 详细介绍:

- 查看 15 Bit 8 kS/s Sigma-Delta ADC 完整数据手册

- 联系 15 Bit 8 kS/s Sigma-Delta ADC 供应商

Block Diagram of the 15 Bit 8 kS/s Sigma-Delta ADC