You are here:

14b-10MSps Cal-SAR ADC

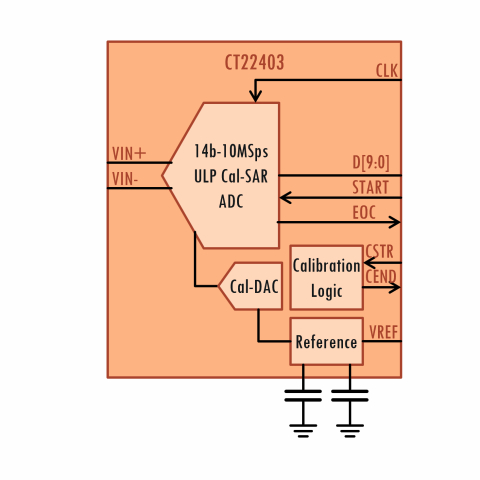

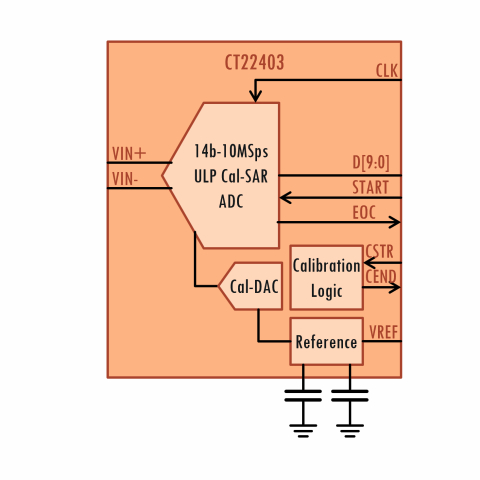

CT22403 is a 14-bit 10 Ms/s Analog to Digital converter.

It is implemented with SAR architecture and offline calibration.

With 15mA total current consumption the Figure of merit of the ADC is 300 fJ/step, that is at the state of the art for its frequency sampling range.

The calibration time at maximum clockfrequency is less than 20 us.

It is implemented with SAR architecture and offline calibration.

With 15mA total current consumption the Figure of merit of the ADC is 300 fJ/step, that is at the state of the art for its frequency sampling range.

The calibration time at maximum clockfrequency is less than 20 us.

查看 14b-10MSps Cal-SAR ADC 详细介绍:

- 查看 14b-10MSps Cal-SAR ADC 完整数据手册

- 联系 14b-10MSps Cal-SAR ADC 供应商

Block Diagram of the 14b-10MSps Cal-SAR ADC

14bits; 10Msps; SAR; ADC; IP

- A/D Converter IP, 10 bits, 10Msps, SAR type, Differential inputs, UMC 0.11um HS/AE process

- A/D Converter IP, 10 bits, 10Msps, SAR type, Differential inputs, UMC 0.11um HS/AE process

- 14b-100KSps Cal-SAR ADC

- General-purpose ADC on TSMC 28nm

- IQ ADC on TSMC 130nm

- Column-parallel high resolution, high speed ADC