You are here:

12-Bit 640MSPS Dual DAC

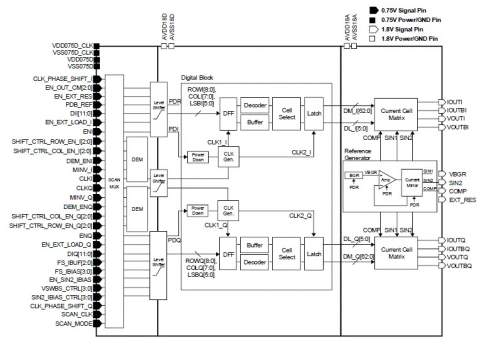

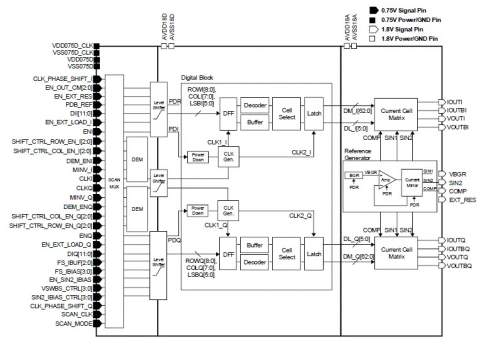

The ll_dac0801s01_ln08lpp_306011 is a 1.8V/0.75V dual supply-voltage I/Q-channel 12-bit digital-to-analog converter (DAC) that supports conversion rate (FS) up to 640MS/s, designed in 8nm CMOS FinFET process. The ll_dac0801s01_ln08lpp_306011 converts 12-bit digital input codes to an analog output signal, providing power-down control. It provides full scale output currents 2.5mA with 200Ω, load for 1.0V differential full scale output voltage. The ll_dac0801s01_ln08lpp_306011 operates with an input clock (CLK). The frequency of CLK is 640MHz with 50% duty cycle. It consists of level shifters, scan mux, dynamic element matching (DEM) logics, power down logics, DFFs, decoders, digital input select logics (Cell Select), buffers, 2nd latches, current cell matrixes, clock generators (CLK gen.), a bandgap reference generator (BGR), an amplifier (AMP) and current mirror blocks.

查看 12-Bit 640MSPS Dual DAC 详细介绍:

- 查看 12-Bit 640MSPS Dual DAC 完整数据手册

- 联系 12-Bit 640MSPS Dual DAC 供应商

Block Diagram of the 12-Bit 640MSPS Dual DAC