You are here:

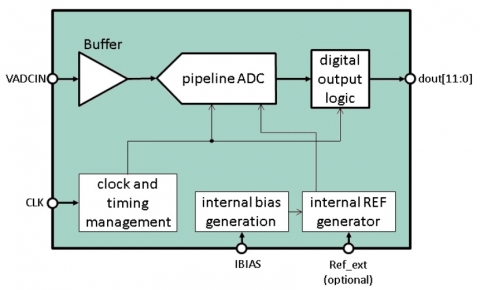

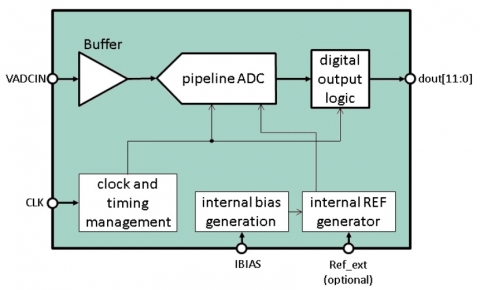

12 Bit 20 MS/s Pipeline ADC

This pipelined ADC can be applied for up to 20MSps sampling frequencies. By using

interleaved switched-capacitor circuitries a CLK signal with half the sampling rate needs to be applied.

This ADC is built as a single-ended architecture and is designed to convert input signals from 0.5 – 2.3V at 3.3V supply voltage with up to 10 MHz input bandwidth with 12 bits resolution.

The ADC IP includes reference voltage generation with buffers and optional high-precision bandgap reference. The accuracy of the ADC is ensured by one-time-trimming of the reference voltages. Power-down mode is available.

The ADC is silicon proven using the XFAB XH035 process. Measurement results and samples are available.

Fraunhofer IIS provides a detailed documentation and

support for the IP integration. Modifications, extensions and technology ports of the IP are available on request

interleaved switched-capacitor circuitries a CLK signal with half the sampling rate needs to be applied.

This ADC is built as a single-ended architecture and is designed to convert input signals from 0.5 – 2.3V at 3.3V supply voltage with up to 10 MHz input bandwidth with 12 bits resolution.

The ADC IP includes reference voltage generation with buffers and optional high-precision bandgap reference. The accuracy of the ADC is ensured by one-time-trimming of the reference voltages. Power-down mode is available.

The ADC is silicon proven using the XFAB XH035 process. Measurement results and samples are available.

Fraunhofer IIS provides a detailed documentation and

support for the IP integration. Modifications, extensions and technology ports of the IP are available on request

查看 12 Bit 20 MS/s Pipeline ADC 详细介绍:

- 查看 12 Bit 20 MS/s Pipeline ADC 完整数据手册

- 联系 12 Bit 20 MS/s Pipeline ADC 供应商

Block Diagram of the 12 Bit 20 MS/s Pipeline ADC