You are here:

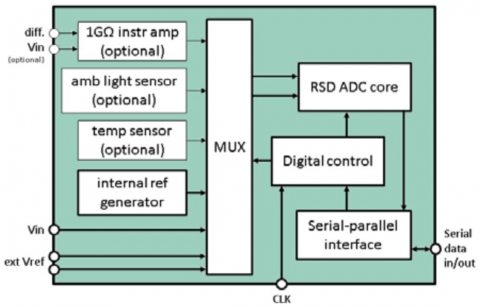

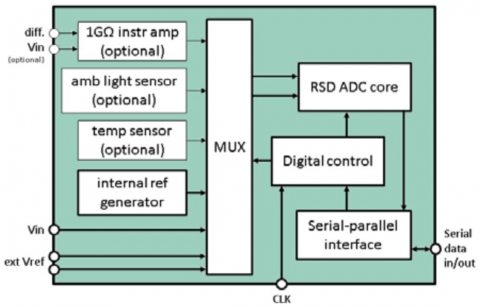

12 Bit 17 kS/s Cyclic ADC

This cyclic ADC, based on redundant-signed-digit (RSD) conversion, is optimized for power efficiency and high accuracy. It provides 12 bit resolution for sampling frequencies up to 17 kS/s for continuous input signals.

This single ended ADC is designed to convert input signals with input swing of 1.9 V. The resolution is configurable (12 bit, 16 bit). Reference voltages can be generated on-chip or applied from outside.

The ADC IP includes serial-to-parallel interface (optional), reference voltage generation and buffers and high-precision trimmed bandgap reference (optional).

Different on-chip sensors (ambient light, temperature) and sensor frontends (instrumentation amplifier) are available.

The ADC is silicon evaluated using the XFAB XH018 process. Measurement results and

samples are available.

Fraunhofer IIS provides a detailed documentation and support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

This single ended ADC is designed to convert input signals with input swing of 1.9 V. The resolution is configurable (12 bit, 16 bit). Reference voltages can be generated on-chip or applied from outside.

The ADC IP includes serial-to-parallel interface (optional), reference voltage generation and buffers and high-precision trimmed bandgap reference (optional).

Different on-chip sensors (ambient light, temperature) and sensor frontends (instrumentation amplifier) are available.

The ADC is silicon evaluated using the XFAB XH018 process. Measurement results and

samples are available.

Fraunhofer IIS provides a detailed documentation and support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

查看 12 Bit 17 kS/s Cyclic ADC 详细介绍:

- 查看 12 Bit 17 kS/s Cyclic ADC 完整数据手册

- 联系 12 Bit 17 kS/s Cyclic ADC 供应商

Block Diagram of the 12 Bit 17 kS/s Cyclic ADC