You are here:

100MHz Fractional-N/SSC PLL

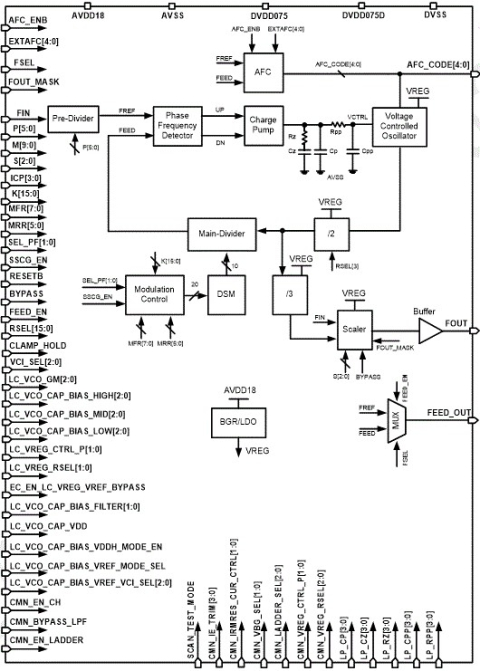

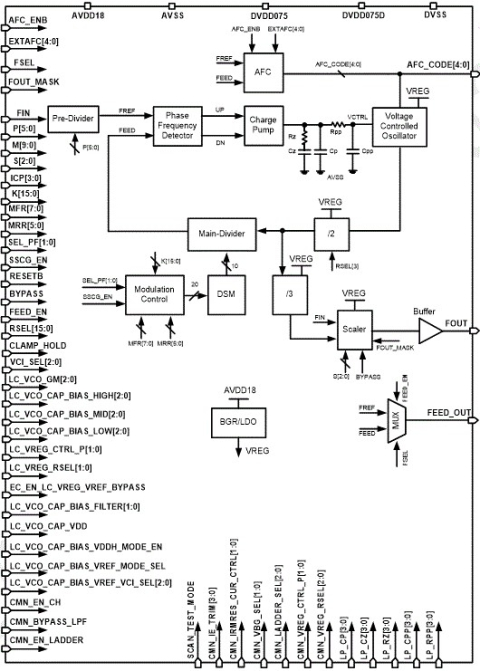

The ll_pll0521s01_ln05lpe_4007011 is a 1.8V/0.85V dual supply-voltage phase locked loop (PLL) with a wide-output-frequency-range for frequency synthesis. It consists of a phase frequency detector (PFD), a charge pump, a voltage-controlled oscillator (VCO), a 6-bit pre-divider, a 10-bit main-divider, a 3-bit scaler, a delta-sigma modulator (DSM) and an automatic frequency control (AFC).

查看 100MHz Fractional-N/SSC PLL 详细介绍:

- 查看 100MHz Fractional-N/SSC PLL 完整数据手册

- 联系 100MHz Fractional-N/SSC PLL 供应商

Block Diagram of the 100MHz Fractional-N/SSC PLL