You are here:

10/25/40/100G MAC/PCS Ethernet IP Core

The 10/25/40/100G MAC IP core is a Low-Latency Ethernet MAC with a latency of 44.8ns in 2749 LUTs for 10Gbit/s and 20.5ns in 2680 LUTs for 25Gbit/s. When combined with the Low-Latency 10/25GPCS, the full packet round trip time for 10Gbit/s is ( MAC Input -> Wire -> MAC Output ) 153.8ns in 5153 LUTs; 25Gbit/s ( MAC Input -> Wire -> MAC Output ) is 128ns in 7930 LUTs.

The IEEE 802.3by compliant 10/25/40/100G MAC/PCS was designed in house at Chevin Technology, to provide an easy path to the integration of protocols such as TCP/IP and UDP protocols in your FPGA, whilst using minimal FPGA resources. The 10/25/40/100G MAC simplifies the synthesis of ultra-fast Duplex 25Gbit/s Ethernet for FPGAs.

The IEEE 802.3by compliant 10/25/40/100G MAC/PCS was designed in house at Chevin Technology, to provide an easy path to the integration of protocols such as TCP/IP and UDP protocols in your FPGA, whilst using minimal FPGA resources. The 10/25/40/100G MAC simplifies the synthesis of ultra-fast Duplex 25Gbit/s Ethernet for FPGAs.

查看 10/25/40/100G MAC/PCS Ethernet IP Core 详细介绍:

- 查看 10/25/40/100G MAC/PCS Ethernet IP Core 完整数据手册

- 联系 10/25/40/100G MAC/PCS Ethernet IP Core 供应商

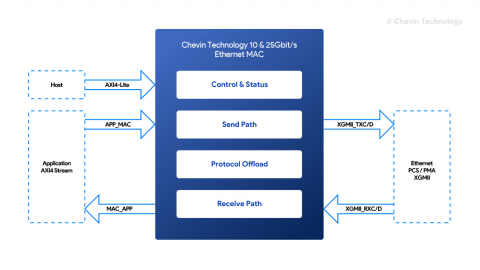

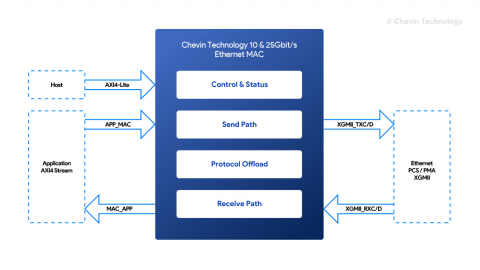

Block Diagram of the 10/25/40/100G MAC/PCS Ethernet IP Core

10G IP

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- USB 3.1 PHY (10G/5G) inTSMC (16nm, 12nm, N7, N6, N5,N3E, N3P)

- 32G Multi Rate SerDes PHY - GlobalFoundries 22FDX

- 32G Multi Rate Long Reach SerDes PHY - GlobalFoundries 12LP and 12LPP

- 32G Multi Rate Very Short Reach SerDes PHY - GlobalFoundries 12LP and 12LPP

- 10G/25G/40G/50G AES Encryption Core