You are here:

10/100/1000 Mbps Ethernet MAC

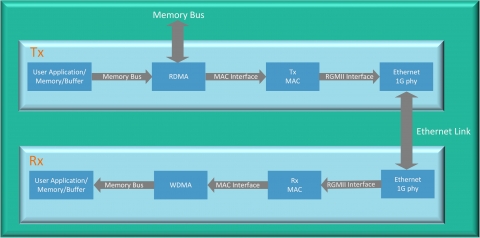

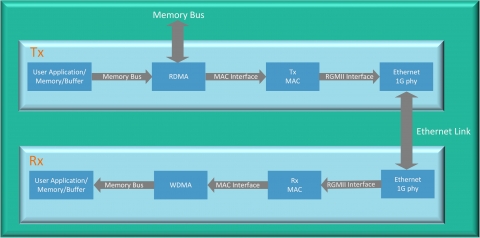

The AL_EMAC_CORE Ethernet MAC Core is hardware implementation of Ethernet protocol defined by IEEE 802.3-2005 Specification. This core transmits and receives Ethernet frames to and from Ethernet network in all three speeds 10/100/1000 Mbps. Both half-duplex and fullduplex mode of operation are supported at all three speeds. The core interfaces to an industry standard external PHY device through RGMII or GMII for Gigabit Ethernet and RGMII or MII for fast Ethernet.

This core is implemented in both Altera Cyclone-III and Xilinx Virtex-4 FPGA. This core also supports pause frame control based on user programmable register setting.

The core has the following modules:

Transmitter

Receiver

MDIO (Management Data Input Output interface)

RGMII,GMII and MII interface

Optional Read and Write DMA Engine

Configuration and Status Registers for Tx, Rx and MDIO

PHY Logic for Ethernet I/O

This core is implemented in both Altera Cyclone-III and Xilinx Virtex-4 FPGA. This core also supports pause frame control based on user programmable register setting.

The core has the following modules:

Transmitter

Receiver

MDIO (Management Data Input Output interface)

RGMII,GMII and MII interface

Optional Read and Write DMA Engine

Configuration and Status Registers for Tx, Rx and MDIO

PHY Logic for Ethernet I/O

查看 10/100/1000 Mbps Ethernet MAC 详细介绍:

- 查看 10/100/1000 Mbps Ethernet MAC 完整数据手册

- 联系 10/100/1000 Mbps Ethernet MAC 供应商

Block Diagram of the 10/100/1000 Mbps Ethernet MAC