You are here:

MIPI CSI-2 Receiver

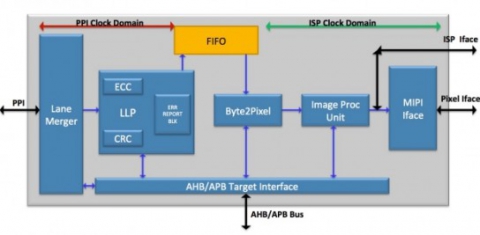

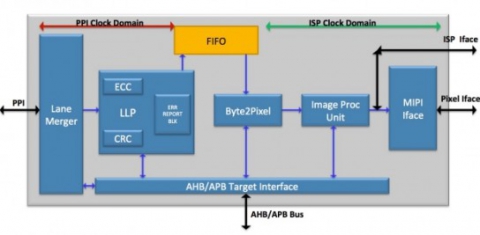

The MIPI CSI-2 Receiver IP is designed to provide MIPI CSI 1.01 compliant high speed serial connectivity for applications processors to corresponding camera modules in mobile platforms. Serial connectivity between this IP and an external the camera module’s CSI transmitter is implemented using 1 to 4 D-PHY lanes, depending on camera sensor resolutions and the resulting bandwidth needs. This IP connects to the D-PHY’s through the PPI interface.

Initial configuration of this IP and its associated D-PHY can be done through programmed IO over an AHB bus, however, other bus interfaces like AXI and OCP can be provided upon request.

This IP performs the data lane merging of image data received on PPI interface from D-PHY. It performs CRC and ECC checks to ensure the integrity of packet payload and header. Based on the user register settings, the IP either forwards or drops the erroneous packets. All forwarded packet payloads are then converted from byte to pixel format, decompressed and output to an external Image Signal Processor (ISP) of the applications processor’s graphics sub-system. All D-PHY Level errors, Packet Level errors and Protocol Decoding Level errors are communicated to the host from a status register.

Initial configuration of this IP and its associated D-PHY can be done through programmed IO over an AHB bus, however, other bus interfaces like AXI and OCP can be provided upon request.

This IP performs the data lane merging of image data received on PPI interface from D-PHY. It performs CRC and ECC checks to ensure the integrity of packet payload and header. Based on the user register settings, the IP either forwards or drops the erroneous packets. All forwarded packet payloads are then converted from byte to pixel format, decompressed and output to an external Image Signal Processor (ISP) of the applications processor’s graphics sub-system. All D-PHY Level errors, Packet Level errors and Protocol Decoding Level errors are communicated to the host from a status register.

查看 MIPI CSI-2 Receiver 详细介绍:

- 查看 MIPI CSI-2 Receiver 完整数据手册

- 联系 MIPI CSI-2 Receiver 供应商

Block Diagram of the MIPI CSI-2 Receiver

CSI-2 controller core IP

- MIPI CSI-2 Controller Core V2

- MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI CSI-2 RX Controller for v2.1

- MIPI CSI-2 TX Controller for v2.1

- MIPI Controller IP, CSI-2 Receiver, High-Speed 80Mbps to 1.5Gbps per data lane, Soft IP