You are here:

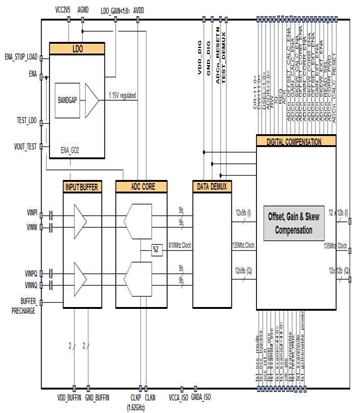

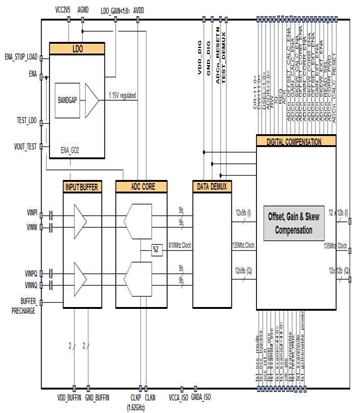

双核 9b-1.62Gsps I&Q 时间交错 SAR 架构 ADC IP

这个IP是一个基于时间交错SAR体系结构的双核I & Q模拟到数字转换器,从生产芯片组中提取,有良好的量产记录。这个设计包含了电源调节器(LDO)、集成参考和数字补偿(增益、偏移和倾斜)。这个IP的模拟输入I & Q是差分模式,输出数据是12x12b总线格式,每个总线对应一个子adc的数据。输出数据的时钟频率是135MHz(Fs/12),也就是采样频率的十二分之一。此外,这个设计的输入缓冲区I & Q和LDO位于G02,ADC和数字补偿位于GO1。

查看 双核 9b-1.62Gsps I&Q 时间交错 SAR 架构 ADC IP 详细介绍:

- 查看 双核 9b-1.62Gsps I&Q 时间交错 SAR 架构 ADC IP 完整数据手册

- 联系 双核 9b-1.62Gsps I&Q 时间交错 SAR 架构 ADC IP 供应商

Block Diagram of the 双核 9b-1.62Gsps I&Q 时间交错 SAR 架构 ADC IP